HDL Coder(硬體描述語言轉碼器)工作流程

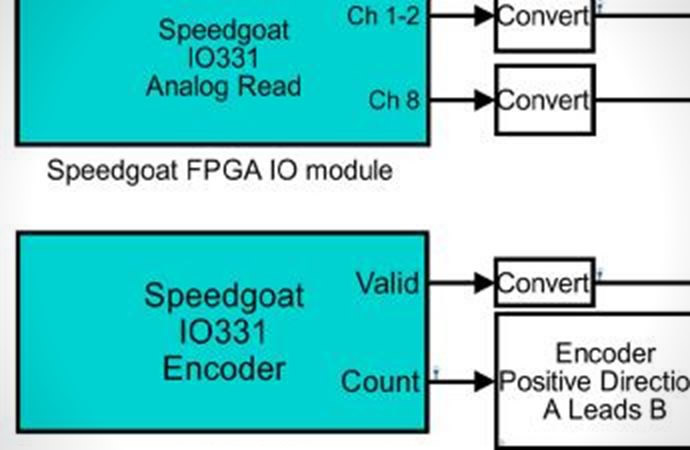

使用者能使用HDL Coder在Speedgoat Simulink可編程FPGA I / O模塊(Speedgoat-Simulink programmable FPGA I/O modules)上運行Simulink®的設計可減少開發時間,並且能夠提早在設計的初期模擬和驗證演算法,這項工作流程還可減少硬體本身的開發週期:

- 自動生成HDL程式碼並整合(synthesize)浮點數或定點數的Simulink模型

- 自動建立即時(real-time)的應用,並將其下載安裝到Speedgoat目標硬體上的FPGA I / O模塊內

- 只需簡單的單擊按鈕就能進行即時的運行應用、記錄(log)數據,以及監視和調整參數

請注意,某些Simulink模塊,可能會有浮點數和定點數的支援限制。HDL Coder所支援的的浮點數非常適合某些演算法,如IIR濾波器、正切函數(tangents),除法以及任何難以收斂的反饋迴路等等。定點數的實現通常更適合於FIR濾波器、FFT和NCO /混合器之類的演算法。

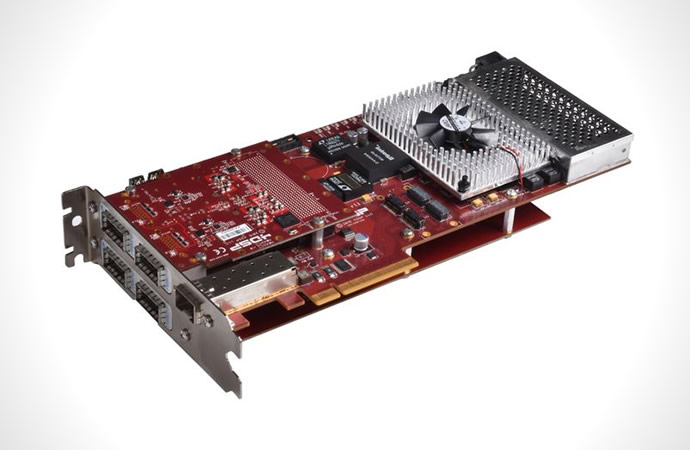

硬體要求

- 至少一個或多個可編程FPGA的Speedgoat即時目標硬體(Real-Time Target Machine)

軟體需求

- MATLAB®, Simulink, MATLAB Coder™, HDL Coder, Simulink Coder™, Simulink Real-Time™

- Xilinx Vivado®

- 適用於Simulink可編程FPGA I / O模塊產品的Speedgoat HDL Coder整合軟體包(Speedgoat HDL Coder Integration Package)

有關軟體和硬體必備條件的更多訊息,請參閱軟體安裝和配置指南。