MATLAB®於FPGA產品級設計與驗證 使用MATLAB與Simulink以硬體架構改善演算法,產生程式碼和進行模型驗證

FPGA、ASIC或SoC專案的眾多團隊成員可以共同制定高抽象等及的早期關鍵決策,並且產生程式碼與模型來推進實現速度。

透過MATLAB和Simulink,你可以:

- 對各種架構選擇進行建模與模擬

- 朝向實現由上而下地改善演算法

- 達到定點量化的覆蓋

- 產生產品等級的RTL和嵌入式C程式碼

- 產生用於數位和類比模擬環境的驗證模型

- 遵循功能安全認證的工作流程

FPGA、ASIC或SoC專案的眾多團隊成員可以共同制定高抽象等及的早期關鍵決策,並且產生程式碼與模型來推進實現速度。

透過MATLAB和Simulink,你可以:

演算法開發人員可以與系統架構師,數位、類比/混合訊號、以及驗證工程師協作,以高抽象層級探索架構選項。這有助於團隊採用分區策略來進行實驗,並借助如硬體微架構和定點量化逐漸改善等實現細節來逐步改善各分區。超過300個模塊支援SystemVerilog、Verilog、VHDL的生成,涵蓋數學運算,以及各種生產驗證的硬體IP模塊與子系統。

透過這套由上而下的流程,你可以持續整合更詳細的模型來進行系統模擬,及早消除功能與性能問題。這項流程還可以幫助你建立級管理系統層級的測試案例套件、量測模型覆蓋率,為後續的順利實現增添信心。

透過HDL Verifier的ASIC測試平台附加功能,你可以直接從MATLAB與Simulink匯出驗證元件,而不需要手寫一個Verilog或VHDL測試平台。你可以直接透過支援C程式碼生成的MATLAB函式或Simulink模型產生模型來加速RTL驗證環境的創建。這幫助你確保精準捕捉參考模型的高階行為及針對RTL模擬的刺激。如果高階設計改變,你可以再次產生模型。

這些驗證元件使用SystemVerilog直接編程接口(Direct Programming Interface,DPI),因此你可以在任何支援SystemVerilog的模擬器使用這些元件。如果你的RTL驗證環境使用了通用驗證方法(Universal Verification Methodolog,UVM),你也可以選擇性地從Simulink產生一個UVM元件。

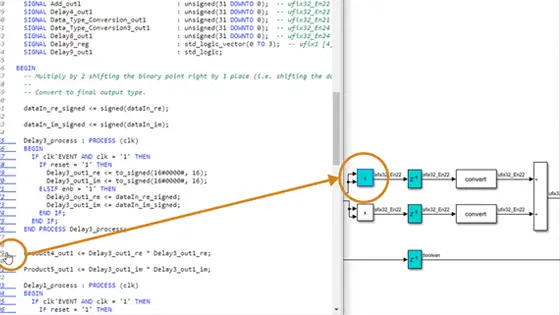

傳統的設計流程通常會在手動編寫特定文件、依據文件以人工編寫程式碼時造成錯誤。要是使用MATLAB和Simulink執行系統層級驗證,你就可以直接從這些經過驗證的實現模型產生適用於FPGA和ASIC設計的HDL和C程式碼。

產生出來的HDL是可讀的,而且可以追蹤回其來源模型,且獨立於目標。你可以控制速度優化(例如配管插入pipeline insertion),面積最佳化(例如來源共享),以及各種編程樣式與結構的選項。透過自動地從選單選擇AMD®與Intel®的合成工具,你可以產生程式腳本來執行任何FPGA或ASIC合成工具。

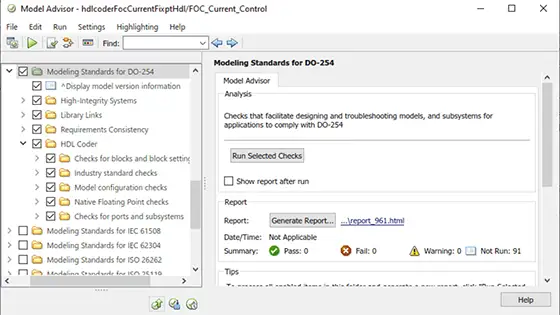

如果你的專案必須符合功能安全標準,FPGA、ASIC與SoC的開發工作流程已包含於專為DO-254、ISO 26262、和IEC 61508推出的套件之中。這些工作流程包含執行Model Adviser來進行內建的檢查,確保你的模型符合相應標準的要求。

產生的HDL和C程式碼具備可讀性,且可以追溯回模型與要求,減輕程式碼審查的負擔。你可以使用各種技巧來協助滿足驗證要求,例如以協同模擬或FPGA迴圈進行背對背測試(back-to-back testing)。