MATLAB® & Simulink®與混合訊號系統

類比和混合訊號系統的分析、設計、與驗證

MATLAB 與 Simulink可協助你進行混合訊號系統的行為建模、快速設計探索、設計之前的分析、驗證等任務。

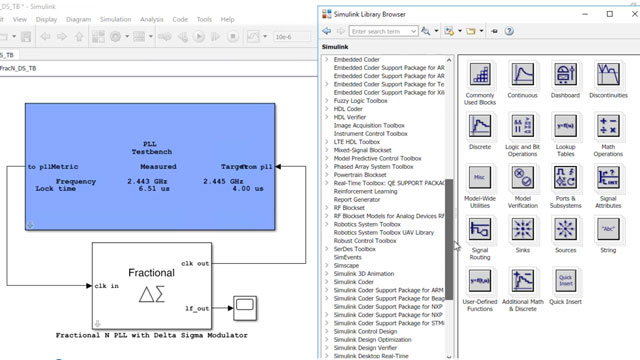

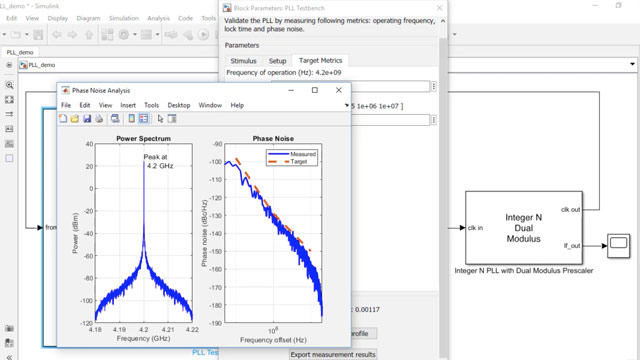

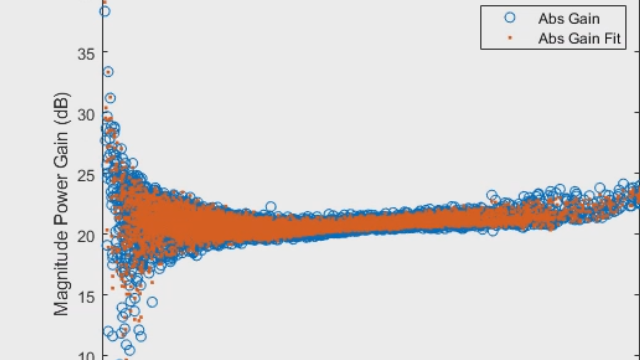

在開始積體電路(integrated circuits,ICs)的設計時,你可以利用Mixed-Signal Blockset™(混合訊號模塊組)提供的PLLs和ADCs模型,建立以資料表單來描繪規格的模塊,並且納入類比損耗。內建的分析工具與量測測試平台(testbenches)可讓驗證工作變得更容易。

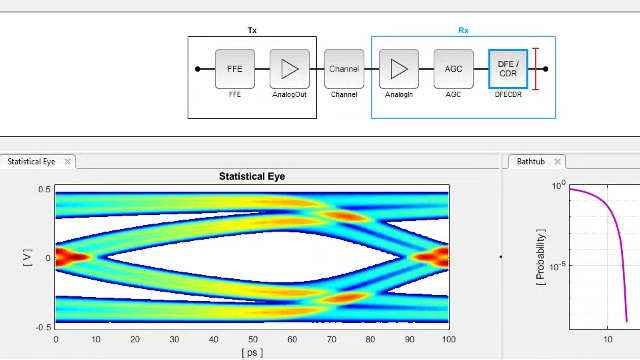

針對像是PCI Expres®、USB、DDR、Ethernet等高速連接的分析,可以使用SerDes工具箱(SerDes Toolbox™)來建立和評估通道等化器的規劃並為通道模擬自動產生IBIS-AMI模型。

- 為PLLs、DACs、ADCs、SerDes、SMPS等混合訊號系統建立行為模型

- 遵照由上而下(top-down)的方法評估類比-數位設計取捨

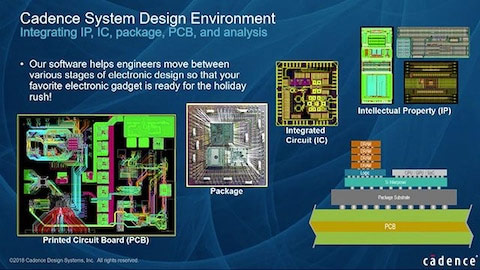

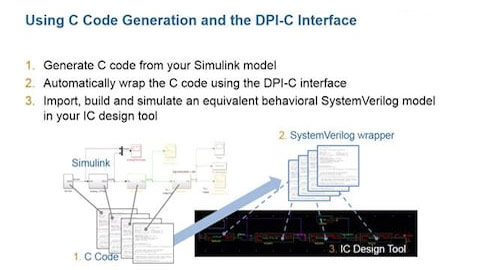

- 透過協同模擬或建立SystemVerilog模組和IBIS-AMI模型來連接系統層級型與EDA工具

- 對高速串列和並行鏈路進行模擬和分析來提高訊號完整性(signal integrity)

- 在生產測試晶片之前進行類比/數位硬體和控制邏輯等設計驗證