MATLAB® & Simulink® 於半導體產業 加速半導體晶片設計與驗證

積體電路(Integrated Circuit,IC)設計工程師使用MATLAB與Simulink來強化並改善積體電路開發過程之中的設計、驗證、原型化等工作任務。

透過MATLAB與Simulink,你可以:

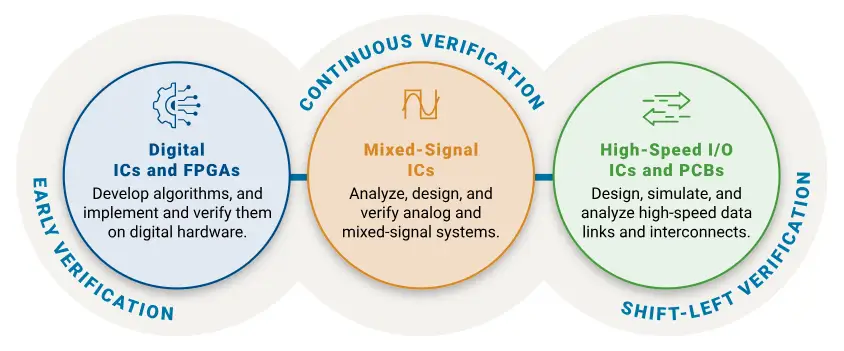

- 利用以模型為基礎的設計來優化架構探索,進行早期驗證,加速驗證流程,縮短開發時間並且降低開發成本。

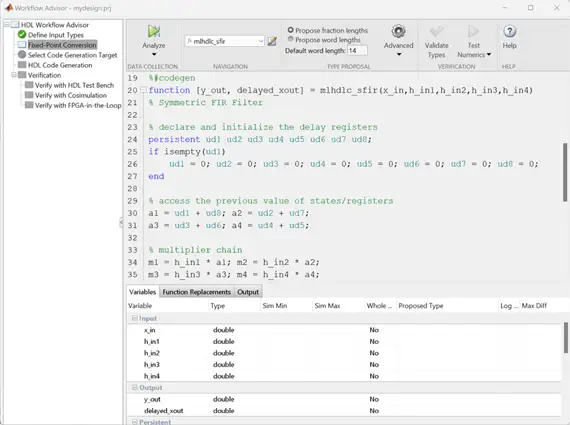

- 產生可合成RTL程式碼與C/C++、HDL、System C,以及IBIS-AMI測試平台與模型來加快原型化、設計實現及驗證。

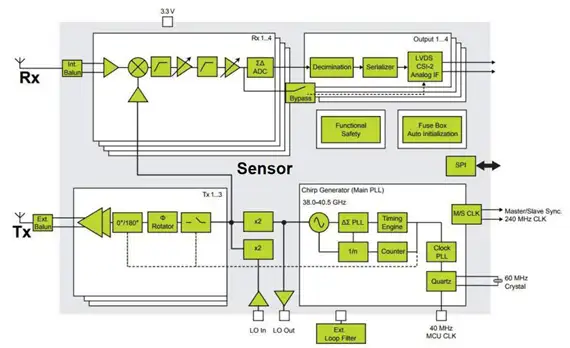

- 在電子設計自動化(Electronic Design Automation,EDA)工作流程之中重複利用現有MATLAB與Simulink模型,將其作為黃金參考模型、激勵產生器和經過檢驗的測試平台。

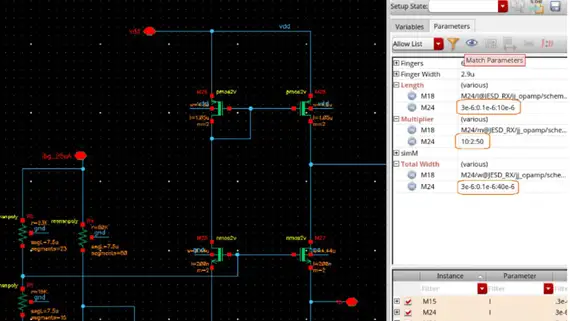

- 透過流程自動化、高階報告、曲線擬合來改善類比及混合訊號設計效率。